#### Department of Electronics & Communication Engg.

**Course : Digital System Design using Verilog.**

Sem.: 6<sup>th</sup> (2017-18)

Course Coordinator: Prof. D. M. Kumbhar

### Digital System Design Using Verilog

#### Module 5 Design Methodology

Portions of this work are from the book, *Digital Design: An Embedded Systems Approach Using Verilog,* by Peter J. Ashenden, published by Morgan Kaufmann Publishers, Copyright 2007 Elsevier Inc. All rights reserved.

# **DESIGN FLOW**

- Digital system design

- Complex expert team

- Systematic design approach manage complexity and interconnection between components

- Design methodology

- Systematic approach of design, verification and preparation for implementation

- Many projects fail lack of control

- Standard design methodology

- Prototype design methodology

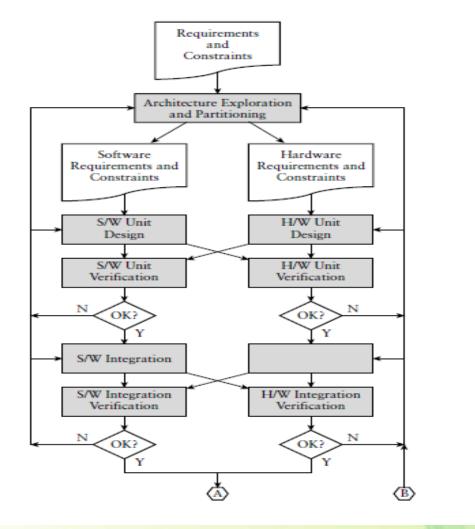

#### **PROTOTYPE DESIGN METHODOLOGY**

4

# Architecture exploration

- Functional requirements and constraints

- Small modifications / new requirement

- Violet/satisfy constraints cost, performance, power consumption, reliability

- Candidate various design approaches

- Architecture exploration refers to the task of abstract modeling and analysis of candidate design

- Partitioning divide problem to sole complexity

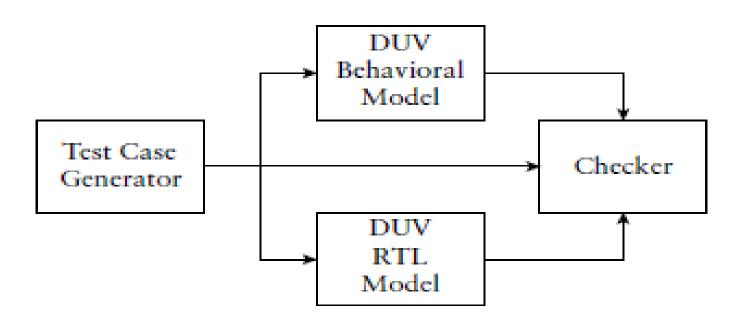

- Logical partitioning

- Physical partitioning

- Hardware software partitioning

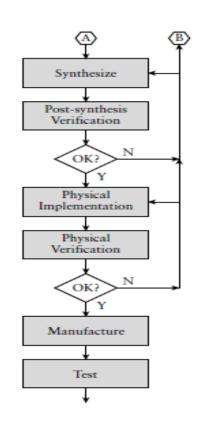

# **Example of Partitioning**

- Road transport monitoring system

- Logical and physical components video from camera, filtering to remove noise, edge detection, shape detection, license plate detection, character recognition for number, logging, n/w interface, control, diagnostic & maintenance task.

# Floor planning

- Physical design types ASISs & FPGA

- ASIC floor planning, placement, routing

- 1. Placement cell & sub cell, closer, external connection

- 2. Routing wire length, conjunction of wiring

- DIP, QFP, PGA, BGA

- 3 Arrangement of power supply, ground & internal connection

- Clock pin & distribution of clock

- FPGA same physical design steps but good planning for interconnections

- Good floor planning reducing interconnections, it's length, faster design, good I/O block connection 7

# **Functional Design**

- Architectural Design top level

- Each block/ component sub component unless complexity manageable

- Develop behavioral model expressing functionality, functional verification, test bench

- Implement given component several approaches

- Reuse components from previous system intellectual property (IP)

less effort, reduced time & verification.

- No reusable IP component from scratch extra efforts, verify functionality

- Core generator EDA tool common functions available such as memories, ALUs, bus interfaces, FSM e.g. Xilinx core gene

- Revision management source code control Multiple design engineers revise code called repository version Completed change affects various parts of code – EDA Verification.

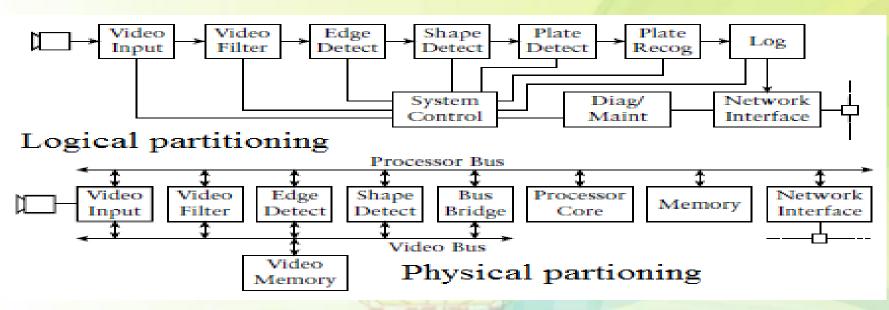

# **Functional Verification**

- Simulation based verification

- Code Generator and checker

- First question, what parts to verify subsystem, top up process

- Second question, what functionality to verify each component

- Coverage functional coverage

- The third question in the verification plan is how to verify. – Directed testing – DUV (simpler components), constrained random testing (complex components)

- Verification language Vera & e

# **Functional Verification**

- Both Directed testing, constrained random testing

- Checker

## **Functional Verification**

- Coverage less

- Formal verification 100% coverage

- Property specification language

- State-space exploration

- Hardware/Software Co-Verification

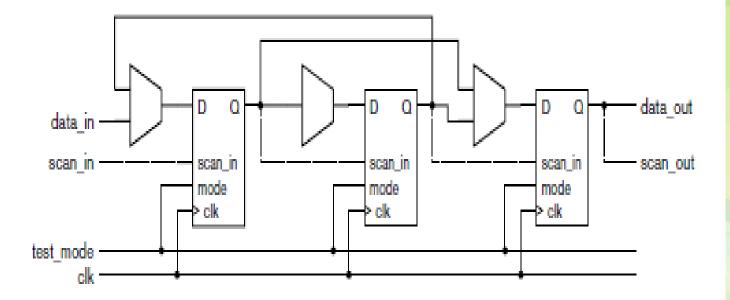

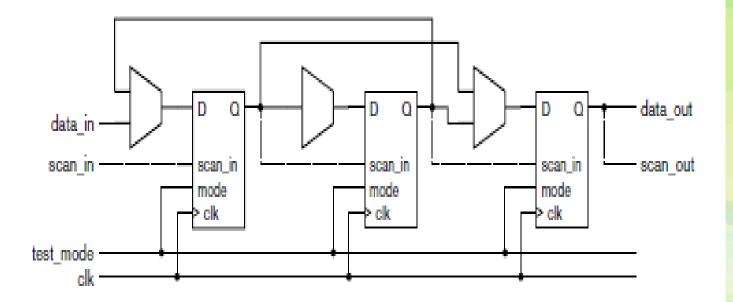

## Scan Chain

FIGURE 10.12 Connection of modified registers in a scan chain.

FIGURE 10.12 Connection of modified registers in a scan chain.

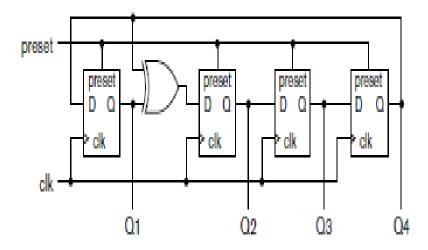

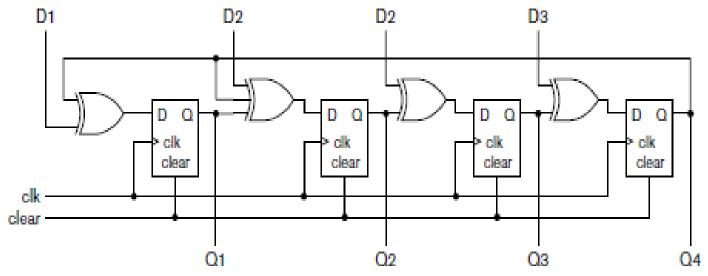

FIGURE 10.17 A 4-bit LFSR for generating pseudo-random test vectors.

$1111 \rightarrow 1011 \rightarrow 1001 \rightarrow 1000 \rightarrow 0100 \rightarrow 0010 \rightarrow 0001 \rightarrow 1100$   $\uparrow_{-0111 \leftarrow 1110 \leftarrow 0101 \leftarrow 1010 \leftarrow 1101 \leftarrow 0011 \leftarrow 0110 \leftarrow 0110}$

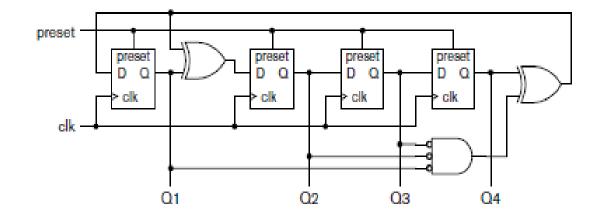

FIGURE 10.18 A 4-bit CFSR for generating pseudorandom test vectors.

$\begin{array}{c} \bullet 1111 \rightarrow 1011 \rightarrow 1001 \rightarrow 1000 \rightarrow 0100 \rightarrow 0010 \rightarrow 0001 \rightarrow 0000 \\ \bullet 0111 \leftarrow 1110 \leftarrow 0101 \leftarrow 1010 \leftarrow 1101 \leftarrow 0011 \leftarrow 0110 \leftarrow 1100 \leftarrow 1100$

#### FIGURE 10.19 A 4-bit MISR

with four inputs from a circuit under test.

-----

and the second second