### **Analog Electronics (15EC32)**

Module-5 Power Amplifiers Class: III Sem

Staff Incharge: S B Akkole Asst. Prof ECE dept. Hirasugar Institute Of Tech. Nidasoshi

### Syllabus.

Power Amplifiers: Definition and amplifier types, Series fed class A amplifier, Transformer coupled class A amplifier, Class B amplifier operation and circuits, Amplifier distortion, Class C and Class D amplifiers.

Voltage Regulators: Discrete transistor voltage regulation - Series and Shunt Voltage regulators

#### **Text Book:**

Robert L. Boylestad and Louis Nashelsky, —Electronics devices and Circuit theory,

A Power amplifier in a stereo, radio or television system is intented to deliver a large voltage and current into a low impedance load such as a loud speaker.

The power amplifiers are classified into:

- 1. Class A power amplifier

- 2. Class B power amplifier

- 3. Class AB power amplifier

- 4. Class C amplifier

- 5. Class D power amplifier

## 1. Class A Power amplifier :-

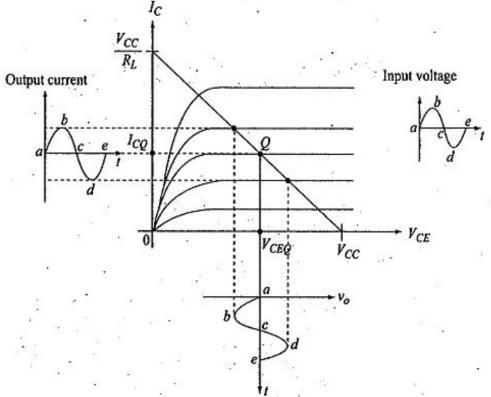

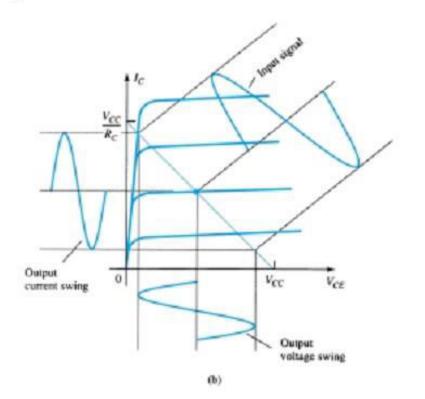

In class A power amplifier, the **Q-point** is **located** at the **centre** of the **load line** as shown in the figure, so that the **output** signal varies over the full cycle of the input signal.

So collector current flows for 360° (FULL Cycle) of the input signal.

### 2. Class B Power amplifier:

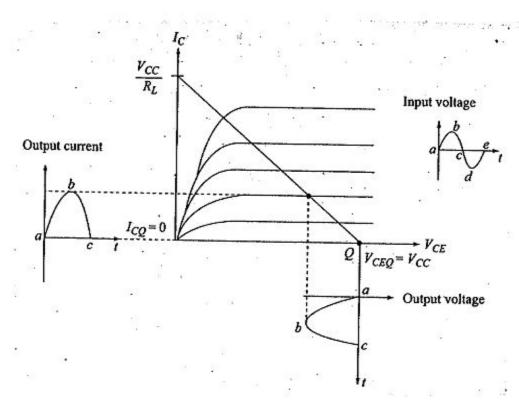

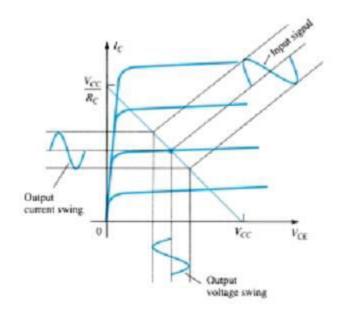

In class B power amplifier, the Q-point is located at cutoff region of the load line as shown in the figure, so that the output signal varies over one half cycle of the input signal.

So collector current flows for 180° (HALF Cycle) of the input signal.

### 3. Class AB Power amplifier :-

In class AB power amplifier, the Q-point and the Input signal are selected such that the output signal is obtained for more than 180° but less than 360°, for a full input cycle.

The efficiency of class AB amplifier is more than Class A but less than Class B amplifier.

# 4. Class C Power amplifier :-

In class C power amplifier, the transistor is biased below cut-off region as shown in figure. The Q-point of the transistor remains in active region for less than a half cycle. So only that much part is reproduced at the output. For the remaining cycle of the input, the transistor remains in cut-off region.

So the collector current flows for less than 180°.

#### 5. Class D Power amplifier :-

A class D amplifier is another class of power amplifier, which is **designed** to **operate** with **PULSE** (digital) signals, which are **ON** for a **short interval** and **OFF** for a **longer interval**.

The **overall efficiency** of **Class D** amplifier is **very HIGH**.

## \* Comparision of power amplifiers :-

| Class                     | A                                                   | В                           | C                 | AB                                                      |

|---------------------------|-----------------------------------------------------|-----------------------------|-------------------|---------------------------------------------------------|

| Operating cycle           | 3600                                                | 1800                        | Less than<br>180° | More than 180° & less than 360°                         |

| Position of Q-point       | Centre of<br>load line                              | On X-axis                   | Below X-<br>axis  | Above X-axis but<br>below the centre of<br>load line.   |

| Input-Output<br>waveforms | √V <sub>1</sub> √V <sub>2</sub> √V <sub>360</sub> ± | 0                           | 180° ±            | V:<br>∘                                                 |

| Efficiency                | Poor i.e 25%<br>to 50%                              | Better,<br>78.5%            | High              | More than class A<br>and Less than Class<br>B amplifier |

| Distortion                | Absent No distortion                                | Present  More than  class A | Highest           | Present                                                 |

# Class-A Power amplifier :-

Depending on how the load is connected at the amplifier output, we have two types of class A power amplifiers as given below:

- 1. Series-fed directly coupled Class A power amplifier.

- 2. Transformer-coupled Class A power amplifier.

### 1. Series-fed directly coupled Class A power amplifier :-

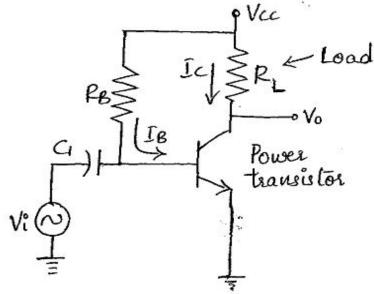

The simple fixed-bias clet connection shown in fig 1) can be used to discuss the main features of a class-A series fed amplifier.

A Re is the load which is connected in series with the collector, so the name series fed amp!

# DC Analysis:-

-Applying KVL to the base loop  $Vcc-I_BP_B-V_{BE}=0$

$I_B = Vcc - 0.7V$ the collector current  $I_C = \beta I_B - O$

fig 1): Series jed class A large signal amplifier. Applying KVL to the collector-emiller Ckt,

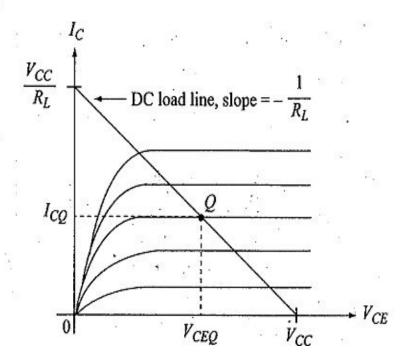

$$T_{c} = \frac{V_{cc}}{R_{L}} - \frac{V_{CE}}{R_{L}}$$

Egn 3 can be written as

Thus, the slope of the dc load line is (-1) 4 the intercept on the current axis is  $\frac{Vcc}{P_L}$ .

### **AC Analysis:**

both the ckt of fig(),

both the dc current &

the ac current flows

through the same load

R. connected in serio

with the collector.

thence the ac load line is the same as the dc load line.

Hence the Q-point can be defined as Q(VCEQ, ICQ)

### **Power Consideration:**-

- -+ For the power amplifier, the input power is supplied from,

- + With no i/p signal (ac signal), the dc current drown is the collector bias current Ica.

i. The de power i/p is given by

# Output Power (Ac power ofp):-

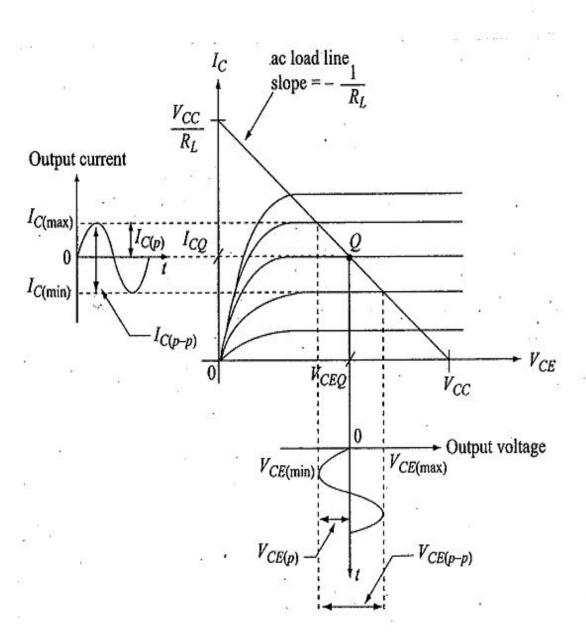

- The ac signal Vi causes the base current to vary around the dc bias current of the collector current around its quiescent level Ica.

- The ac ilp signal results in accurrent + ac vtg signals.

- The larger the ilp signal, the larger is the ofp swing.

The ac power delivered to the load (Pc) can be expre-

- ssed in a no of ways:

- i) Using RMS signal values.

- ii) Using peak signals values.

- iii) Using peak-to-peak signal values

- iv) Using Maximum 4 minimum values.

Using PMS signals: The ac power delinered to the load (Rc) is given Po (ac) = VCE (Ims). Icums) - 1. Po(ac) = Icums). PL Polac) = VCE cems) · VCE cems) Po (ac) = VCE (ums) /PL

ii) Using peak signals :-

W.k.t.

Irus = Im

Polac) = Vceip)

2PL

Pocac) = VCE(p). VCE(p)

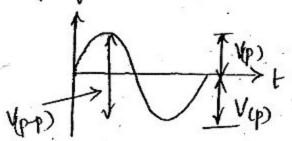

iii> Using peak- to - peak signals: -

$$V_{(p-p)} = V_{(p)} + V_{(p)}$$

$$V_{(p-p)} = 2V_{(p)}$$

$$V_{(p)} = V_{(p-p)}$$

$$I(p-p) = I(p) + I(p)$$

$$I(p-p) = 2I(p)$$

$$I(p-p) = \frac{I(p-p)}{2}$$

Po (ac) =

$$V_{CE}(sms)$$

,  $I_{C}(sms)$

=  $\frac{V_{CE}(p)}{\sqrt{2}}$ .  $\frac{I_{C}(p)}{\sqrt{2}}$

=  $\frac{V_{CE}(p)}{2}$ .  $I_{C}(p)$

$$Po(ac) = \frac{VcE(p-p) \cdot Ic(p-p)}{Q}$$

$$w.k.t.$$

$$V(E(p) = \frac{V(E(p-p))}{2}$$

$$I((p) = \frac{I(p-p)}{2}$$

$$P_0(ac) = I_{c(p-p)}.P_L \cdot \frac{I_{c(p-p)}}{8} \times P_L$$

The efficiency of an amplifier represents the amount of ac power delivered or transferred to the load, from the dc source.

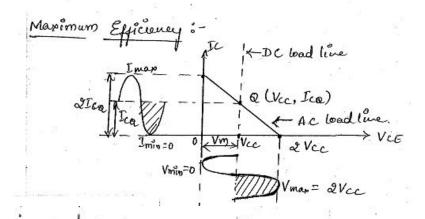

Maximum efficiency:-

Vmax = Vcc & Vmin = 0

Imax = 2Ica & Imin = 0

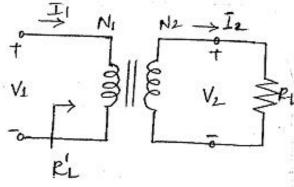

### **Properties of Transformer:**

It is assumed that the transformer, it is assumed that the transformer is ideal & there are no losses in the transformer.

- the winding resistances are assumed to be zero.

let

NI -> No of turns on primary

N2 -> No of Turus on secondary

V, → Voltage applied to primary

V2 → secondary voltage.

I, → primary current

I2 -> Secondary current.

# 1> Turus ralio: -

The salio of no of turns on secondary to the no of turns on primary is called turns salio of the transformer denoted by 'n'.

N2: 1 82 N1: 1

ii) Voltage transformation :-

one side to other side proportional to the turns ratio. The transformer can be step up or step down transformer.

$$\frac{V_2}{V_1} = \frac{N_2}{N_1} = n$$

$$\frac{V_1}{V_1} = \frac{N_1}{N_2}$$

iii Current Transformation:

$$\frac{I_2}{I_1} = \frac{N_1}{N_2} = \frac{1}{D}$$

$$4 P_{L} = \frac{V_{1}}{\Gamma_{1}}$$

changed by a transformer, an impedance seen from either side can also be changed.

where Ri's the load reflected at the primary.

$$\frac{V_1 I_2}{V_2 I_1} = \frac{N_1^2}{N_2^2} \qquad -3$$

$$\frac{V_1/I_1}{V_2/I_2} = \left(\frac{N_1}{N_2}\right)^2 - 6.$$

substituting eq. 3 + 4 in eq. 6 we have  $\frac{P_L}{P_L} = \left(\frac{N_1}{N_2}\right)^2$

or

$$P_L = P_L \left(\frac{N_1}{N_2}\right)^2$$

or  $P_L = \frac{P_L}{n^2}$

PL>PL can be achieved by choosing N,>N2 ie we have to use a step down transformer of appropriate turns ratio.

## ADVANTAGES :-

- The efficiency of the operation is higher than directly coupled amplifies.

- The impedance matching required for maximum power transfer is possible.

- There is perfect isolation b/n the a.c power developed across the load of the d.c 1/p power due to transformer.

## DISADVANTAGES :-

- Due to the inductance of the transformer winding, the frequency response is poor compared to series-fed amplifies

- The circuit is bulky, heavy & costly due to the transformer.

- I The designing of turns ratio & other parts of the cht is complicated compared to series-fed amply.

1. Explain the operation of the transformer coupled class-A power amplifier. Prove that the maximum power efficiency is 50%.

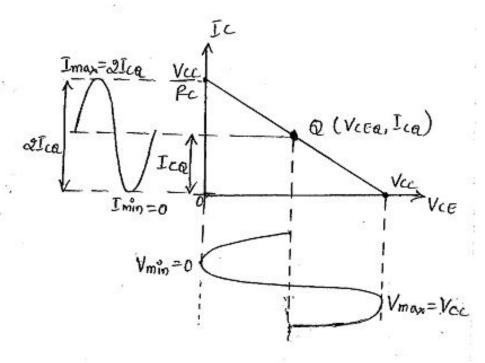

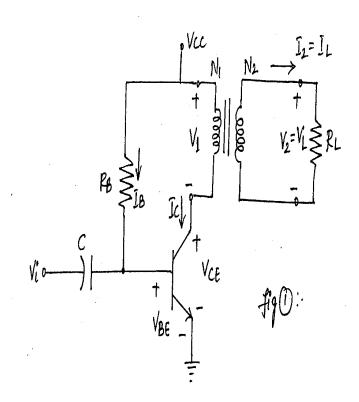

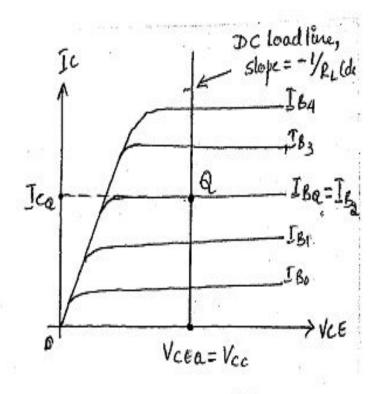

DC operation:

\* H'is assumed that the winding resistances are zero ohms.

There is no de voltage drop across primary of transformer

w.t.t the slope of dc load line is reciprocal of the d.c. resistance in the collector ckt  $\left(\frac{1}{R_{dc}}\right) = \frac{1}{\delta} = \infty$ .

Applying KVL to the collector ckt

Vcc-VcE = 0

· · Vec = Vee

VCEQ = Vcc | - This is the dc bias vtg VCEQ for the transistor.

- Hence the d.c load line is a vertical straight line passing through a vtg point on the x-axis which is  $V_{CEQ} = V_{CC}$ .

# DC I/P Power :-

The de current drawn u collector bias current Ica

fig 2 : DC load line

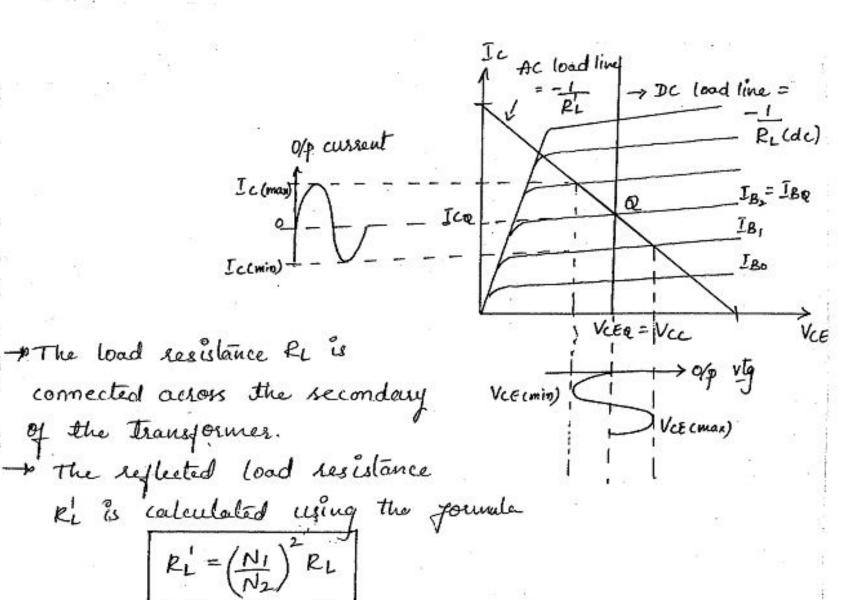

## AC Analysis :-

### Expression for AC O/P power :-

let

$$V_{lm} = peak value of primary voltage.$$

In = peak value of primary current.

Substituting eq? (2) in (1), we get

$$P_{ac} = \frac{1}{2} \cdot \frac{(V_{max} - V_{min})}{2} \cdot \frac{(I_{max} - I_{min})}{2}$$

Similarly the ac power delivered to the load on secondary can be calculated using secondary quantities.

let

Vem = peak value of secondary or load vtg.

Dem = peak value of secondary or load current.

### Maximum Efficiency:-

For maximum n. Pout is also maximum.

Maximum theortical

efficiency:

% n = 50 (VCEmax VCEmin)

VCEmax + VCEmin)

## ADVANTAGES :-

- The efficiency of the operation is higher than directly coupled amplifies.

- The impedance mathing required for maximum power transfer is possible.

- There is perfect isolation b/n the a.c power developed across the load of the d.c i/p power due to transformer.

# DISADVANTAGES :-

- Due to the inductance of the transformer winding, the frequency response is poor compared to series-fed amplifies

- transformer.

- the designing of turns ratio & other parts of the cht is complicated compared to series-fed amply.

### Class B-POWER AMPLIFIERS

# Class-B power Amplifiers:

- In class B amplifier the collector current flows only for a half cycle of the full cycle lip signal.

- To get a full cycle across the load, a pair of transistors are used in class-B operation.

- the two transistors conduct in alternate half cycles of the ilp signal & a full cycle is obtained across the load.

- The two transistors are identical in characteristics 4 are called matched transistors.

- n-p-n, there are two types of class-B amplifiers:

- 1) Puss-pull class-B or where the transistors are of some type ie. either p-n-p or n-p-n.

- Joan à complementary pair ie. one n-p-n & other p-n-p.

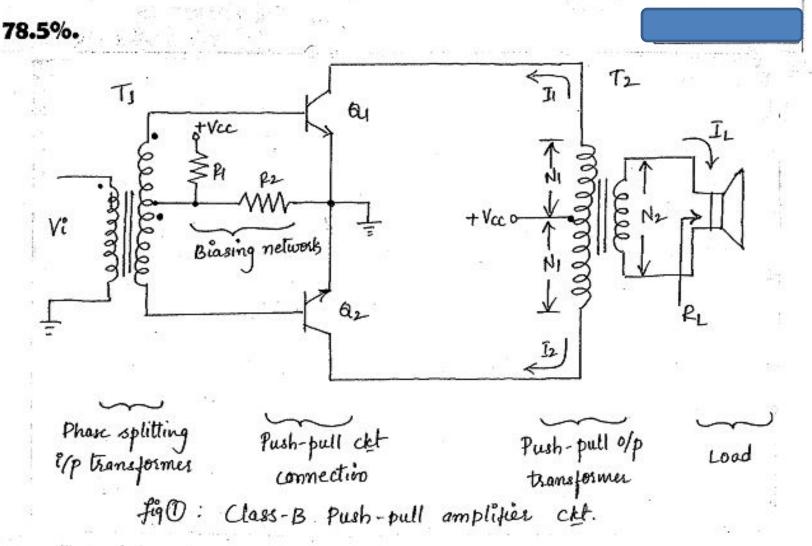

2. Draw the circuit diagram and explain the operation with relevant waveforms of class-B push pull amplifier. Also show that the maximum conversion efficiency of class-B push-pull amplifier is

- 1) Two-centre tapped transformer (T, FTz)

1) Two identical transistors Q, f Qz (n-pn)

- The transformer 'Ti' is an ilp transformer of is called phase splitter. It is required to produce two signal voltages, which are 180° out of phase with each other.

- These two signal vollages, with opposite polarity, drive the i/p of transistor a, + Q2. (ib, + ib2)

- → The transformer T2 is an o/p transformer t is required to couple a.c. o/p signal from the collector to load.

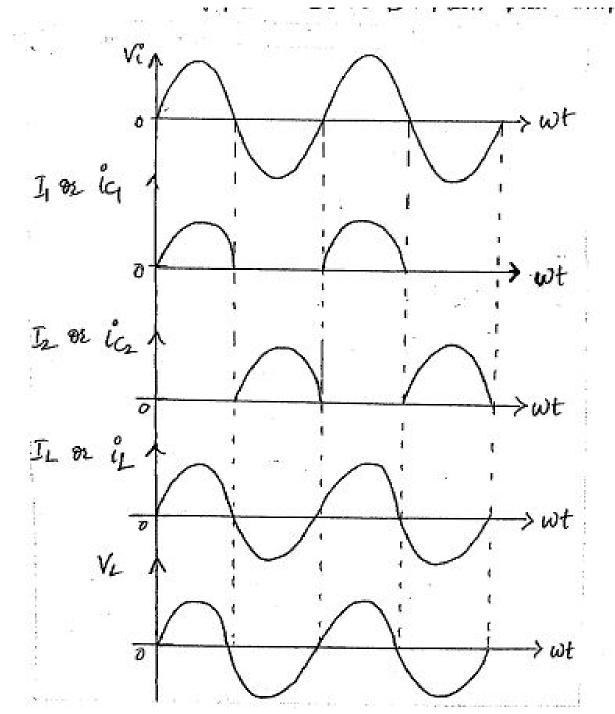

Operation !-During +ve half cycle of the ilp signal, the base of transistor a, is +ve & that of as is -ve. As a sesult of this, or conducts, while the transistor as is Off.

- When the ip signal goes -ve, & turns OFF + &2 conduct Thus, at an instant, only one transistor in the circuit

- Each transistor handles one-half of the isp signal.

The Op transformer joins these two half-signals & produces

- a full eycle in the load.

- transistors is never perfect & hence the 0/9 is distorted.

- The load current is given by

$$\overline{I_L} = \overline{I_1} - \overline{I_2} \qquad \text{or} \qquad [i_L = ic_1 - ic_2]$$

- During one half cycle, one part of the circuit pushes the signal high & during other half eyele, the other part pulls the signal low. Hence the name push-pull amp!

- The class-B push pull ampl" is known as double ended class-B ampl"

### **ADVANTAGES :-**

- 1) The efficiency is higher than class A amplifier (78.5%)

- 22 When there is no l/p signal, the power dissipation is zero.

- 3> Impedance matching can be achieved perfectly due to the presence of olp transformer.

- 4> Even harmonics are absent in the off. This reduces harmonice distortion.

- 57 Because of the absence of even harmonies in the o/p, the cht gives more o/p power per transistor for a given amount of distortion.

### **DISADVANTAGES** :-

- 1> Two center-top transformers are necessary.

- 2) The transformers make the circuit bulky, heavy & costlier compared to other power amplifiers.

- 3> Frequency response is poor due to the presence of inductance of the transformers.

- 47 H is difficult to find the exact centre-tap in the two

transformers.

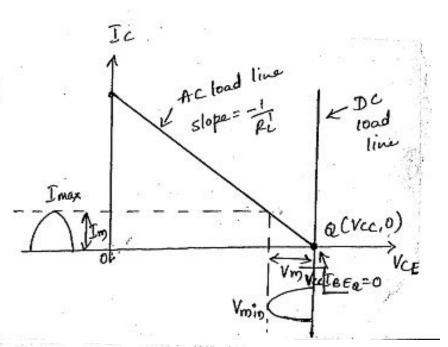

### DC operation :-

The dc biasing point is Q-point is adjusted on the x-axis such that  $V_{CEQ} = V_{CC}$  4  $I_{CEa} = 0$ .

Thence co-ordinates of the Q-point are ( $V_{CC}$ , 0)

DC power i/p:-

with a peak value of Im or Icep.

Thus the average current in each transistor is I'm.

- Since there are two transistors, the dc current drawn from the supply Vcc, by both the Transistors is  $I_{dc} = 2 \left( average current in each transistor \right)$

The dc power i/p to the power amplifier is given by

### **AC operation:**

The ac power ofp is given by

### Maximum Efficiency:-

$$W.k.+ V_m = V_{max} - V_{min}$$

$= V_{cc} - 0$

$V_m = V_{cc}$

#### Power dissipation :-

$$Pd = \frac{2 \text{ Vcc. } Vm}{\pi} - \frac{Vm}{2} \cdot \frac{Vm}{P_L^{'}}$$

$$Pd = \frac{2}{\pi} \cdot \frac{\text{Vce. } Vm}{P_L^{'}} - \frac{V_m^2}{2 P_L^{'}}$$

- ohen no i/p signal.

- -> But in Class B amplifier, when i/p signal is zero, Vm=0 hence the power dissipation is zero & not maximum.

$P_{dc} = \frac{2}{\pi} V_{cc} \cdot I_m$   $P_{ac} = \frac{V_m \cdot I_m}{2}$

### Maximum Power dissipation :-

-\* The condition for maximum power dissipation can be obtained by differentiating the egro w.r.t Vm & equating it to zero.

$$Pd = \frac{Q}{\pi} \cdot \frac{VccVm}{PL} - \frac{V_m^2}{QPL}$$

$$\frac{dP_d}{dV_m} = \frac{2}{\pi} \frac{V_{CC}}{R_L^i} - \frac{2V_m}{2R_L^i} = 0$$

$$\frac{2 \text{ Vcc}}{\pi R_{L}'} = \frac{2 \text{ Vcc}}{2 \text{ RL}'}$$

$$V_{m} = \frac{2 \text{ Vcc}}{\pi R_{L}'}$$

$$V_{m} = \frac{2 \text$$

Substituting eq. (Pa) max =

$$\frac{2 \text{Vcc}}{\pi \text{RL}^{1}} \cdot \frac{2 \text{Vcc}}{\pi} - \left(\frac{2 \text{Vcc}}{\pi}\right)^{2} \cdot \frac{1}{2 \text{RL}^{1}}$$

$$= \frac{4}{\pi^{2}} \cdot \frac{\text{Vcc}}{\text{RL}^{1}} - \frac{2 \text{Vcc}}{\pi^{2}} \cdot \frac{1}{2 \text{RL}^{1}}$$

$$= \frac{4}{\pi^{2}} \cdot \frac{\text{Vcc}}{\text{RL}^{1}} - \frac{2}{\pi^{2}} \cdot \frac{\text{Vcc}}{\text{RL}^{1}}$$

$$= \frac{4}{\pi^{2}} \cdot \frac{\text{Vcc}}{\text{RL}^{1}} - \frac{2}{\pi^{2}} \cdot \frac{\text{Vcc}}{\text{RL}^{1}}$$

$$(Pd)_{\text{max}} = \frac{2}{\pi^2} \frac{V_{\text{cc}}^2}{P_L^2}$$

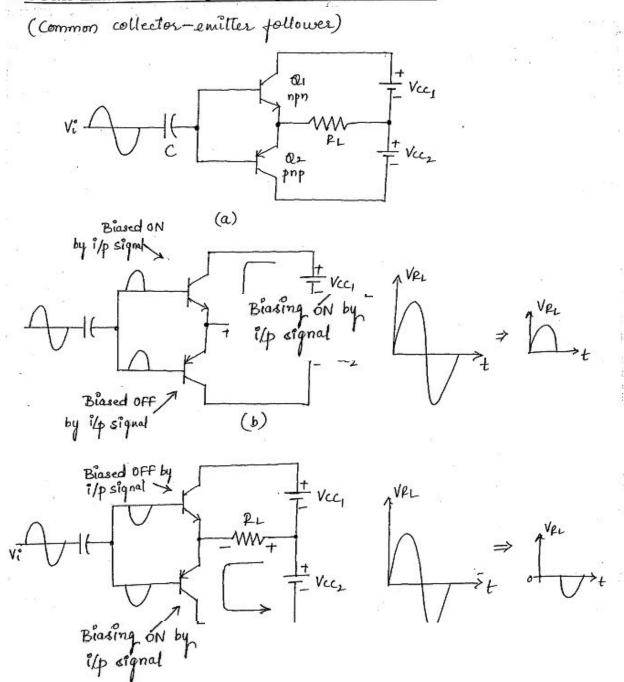

### COMPLEMENTARY Symmetry Class B Amplifier :-

- The transister a, is n-p-n while az is p-n-p type.

\* The circuit is driven from a dual supply of I vcc.

\* During +ve half cycle of the l/p signal, the transistor QI will be biased into conduction, resulting in a half cycle signal across the load.

During -ve half cycle of the i/p signal, the p-n-p transistor of will be biased into conduction resulting in -ve half eycle across the load Re.

\* Thus for a complete cycle of i/p, a complete cycle of o/p signal is obtained across the load.

## Mathematical Analysis: -

\* All the results derived for Push-pull transformer coupled class-B amplifier are applicable to the complementary class B amplifier.

\* The only change is that as the o/p transformer is not present, hence in the expressions, & value must be used as it o is, instead of &!

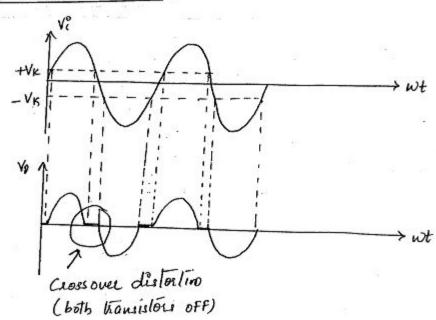

Crossover distortion

(d)

Advantages: 1> As the circuit is transformerless, its weight, size of cost are less.

common collector configuration, impedance matching is

3) The prequency response improves due to transpormenless Class B amplifier Ckt.

Disadvantages

17 The circuit needs two separate voltage supplies.

distorted to cross-over distortion.

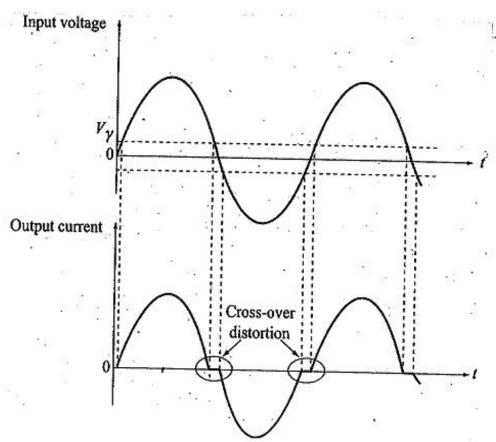

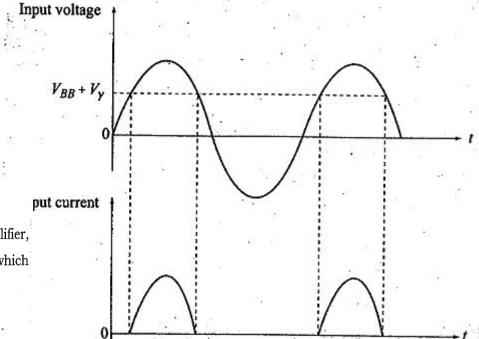

#### Cross-over distortion :-

- Junction must be forwards biased.

- The junction is cannot be forward brased I'll The voltage applied becomes greater Than cut-in vig (VK) of The junction, which is generally 0.74 for silken + 0.24 for Ge.

- Thus when i/p is less than 0.7V, the base-emitter junction is reverse biased, the collector current remain zero & transistor remains in cut-of region.

- thence There is a period b/n the crossing of the half cycles of the i/p signal, for which none of the transistors is active 4 the 0/p is zero.

- Hence the opp signal gets distoited.

- -> such distortion in the opp signal is called cross-over distortion.

- Due to cross-over distortion each transistor conducts for less than a half cycle rather than The complete half cycle.

# Comparision of Push Pull and Complementary symmetry circuits:

| S1<br>No. | Push Pull Class B                                                                     | Complementary symmetry class B                                                    |  |  |

|-----------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|

| 1.        | Both the transistors are either p-n-p or n-p-n.                                       | Transistors are complementary type i.e. one <i>n-p-n</i> and other <i>p-n-p</i> . |  |  |

| 2.        | The <b>transformer</b> is <b>used</b> to connect the load as well as input.           | The circuit is <b>transformer less</b> .                                          |  |  |

| 3.        | The impedance matching is possible due to the output transformer.                     | The impedance matching is possible due to common collector circuit.               |  |  |

| 4.        | Frequency response is <b>poor</b>                                                     | Frequency response is <b>improved</b>                                             |  |  |

| 5.        | Due to transformers, the circuit is <b>bulky</b> , <b>costly</b> and <b>heavier</b> . | As transformer less, the circuit is <b>not bulky</b> and <b>less costly</b> .     |  |  |

| 6.        | Dual power supply is not required.                                                    | Dual power supply is required.                                                    |  |  |

| 7.        | The efficiency is higher than class A i.e 78.5%                                       | The efficiency is higher than the push pull i.e >78.5%                            |  |  |

| 8.        | Circuit is complicated                                                                | Circuit is simple.                                                                |  |  |

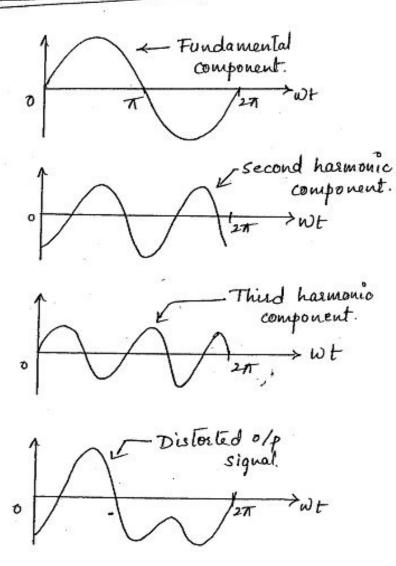

- which are not present to the i/p signal is called as harmonic distortion.

- The component with frequency same as its signal is called fundamental frequency.

- Additional frequency components which are integer multiples of fundamental frequency are called harmonics.

- The jourier analysis of the olp signal reveals that as the order of the harmonic increases, its amplitude decreases of frequency increases.

### **Expression for % harmonic distortion :-**

where Bost amplitude of the fundamental frequency component.

Bn - amplitude of the not frequency component.

Eg > % second harmonic distortion is given by  $D_2 = |\frac{32}{|B_1|} \times 100\%$

THD =

$$\sqrt{D_2^2 + D_3^2 + \dots D_n^2} \times 100$$

$\sqrt{0}$

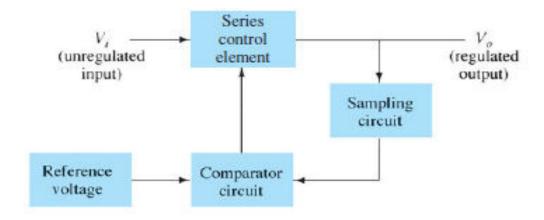

#### 15.5 DISCRETE TRANSISTOR VOLTAGE REGULATION

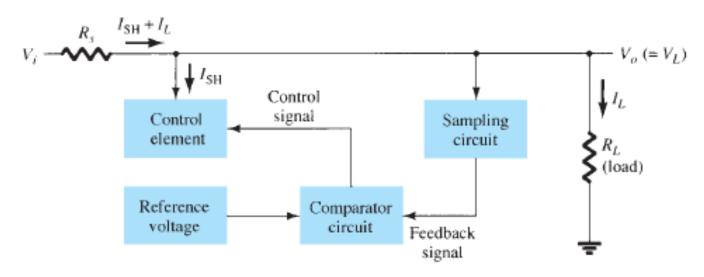

Two types of transistor voltage regulators are the series voltage regulator and the shunt voltage regulator. Each type of circuit can provide an output dc voltage that is regulated or maintained at a set value even if the input voltage varies or if the load connected to the output changes.

#### Series Voltage Regulation

The basic connection of a series regulator circuit is shown in the block diagram of Fig. 15.12. The series element controls the amount of the input voltage that gets to the output.

FIG. 15.12

Series regulator block diagram.

The output voltage is sampled by a circuit that provides a feedback voltage to be compared to a reference voltage.

- If the output voltage increases, the comparator circuit provides a control signal to cause the series control element to decrease the amount of the output voltage—thereby maintaining the output voltage.

- If the output voltage decreases, the comparator circuit provides a control signal to cause the series control element to increase the amount of the output voltage.

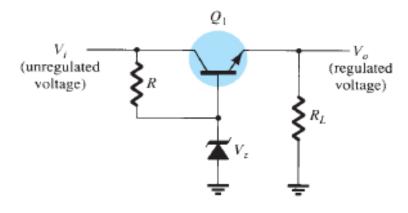

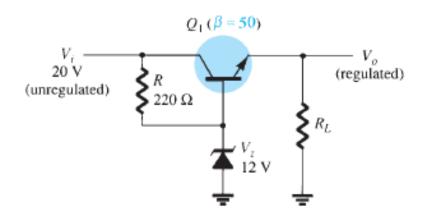

**Series Regulator Circuit** A simple series regulator circuit is shown in Fig. 15.13. Transistor  $Q_1$  is the series control element, and Zener diode  $D_Z$  provides the reference voltage. The regulating operation can be described as follows:

FIG. 15.13 Series regulator circuit.

- If the output voltage decreases, the increased base-emitter voltage causes transistor Q<sub>1</sub>

to conduct more, thereby raising the output voltage—maintaining the output constant.

- If the output voltage increases, the decreased base-emitter voltage causes transistor

Q<sub>1</sub> to conduct less, thereby reducing the output voltage—maintaining the output

constant.

**EXAMPLE 15.8** Calculate the output voltage and the Zener current in the regulator circuit of Fig. 15.14 for  $R_L = 1 \text{ k}\Omega$ .

FIG. 15.14 Circuit for Example 15.8.

#### Solution:

$$V_o = V_Z - V_{BE} = 12 \text{ V} - 0.7 \text{ V} = 11.3 \text{ V}$$

$V_{CE} = V_i - V_o = 20 \text{ V} - 11.3 \text{ V} = 8.7 \text{ V}$

$I_R = \frac{20 \text{ V} - 12 \text{ V}}{220 \Omega} = \frac{8 \text{ V}}{220 \Omega} = 36.4 \text{ mA}$

For  $R_L = 1 \text{ k}\Omega$ ,

$$I_L = \frac{V_o}{R_L} = \frac{11.3 \text{ V}}{1 \text{ k}\Omega} = 11.3 \text{ mA}$$

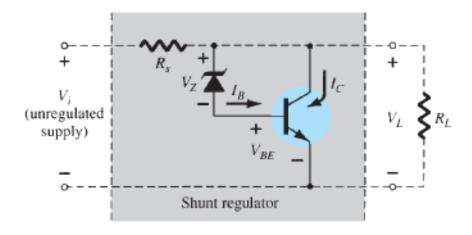

### **Shunt Voltage Regulation**

A shunt voltage regulator provides regulation by shunting current away from the load to regulate the output voltage. Figure 15.20 shows the block diagram of such a voltage regulator. The input unregulated voltage provides current to the load. Some of the current is pulled away by the control element to maintain the regulated output voltage across the load. If the load voltage tries to change due to a change in the load, the sampling circuit provides

FIG. 15.20

Block diagram of shunt voltage regulator.

a feedback signal to a comparator, which then provides a control signal to vary the amount of the current shunted away from the load. As the output voltage tries to get larger, for example, the sampling circuit provides a feedback signal to the comparator circuit, which then provides a control signal to draw increased shunt current, providing less load current, thereby keeping the regulated voltage from rising.

**Basic Transistor Shunt Regulator** A basic shunt regulator circuit is shown in Fig. 15.21. Resistor  $R_S$  drops the unregulated voltage by an amount that depends on the current supplied to the load  $R_L$ . The voltage across the load is set by the Zener diode and transistor base-emitter voltage. If the load resistance decreases, a reduced drive current to the base of  $Q_1$  results, shunting less collector current. The load current is thus larger, thereby maintaining the regulated voltage across the load. The output voltage to the load is

$$V_L = V_Z + V_{BE} (15.19)$$

FIG. 15.21

Transistor shunt voltage regulator.

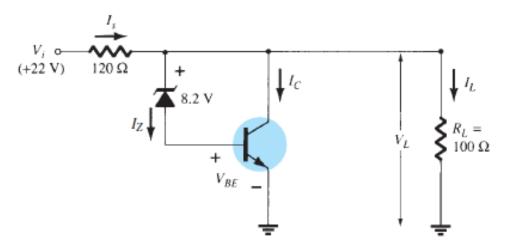

**EXAMPLE 15.11** Determine the regulated voltage and circuit currents for the shunt regulator of Fig. 15.22.

FIG. 15.22 Circuit for Example 15.11.

**Solution:** The load voltage is

Eq. (15.19):

$$V_L = 8.2 \text{ V} + 0.7 \text{ V} = 8.9 \text{ V}$$

For the given load,

$$I_L = \frac{V_L}{R_L} = \frac{8.9 \text{ V}}{100 \Omega} = 89 \text{ mA}$$

With the unregulated input voltage at 22 V, the current through  $R_S$  is

$$I_S = \frac{V_i - V_L}{R_S} = \frac{22 \text{ V} - 8.9 \text{ V}}{120} = 109 \text{ mA}$$

so that the collector current is

$$I_C = I_S - I_L = 109 \,\text{mA} - 89 \,\text{mA} = 20 \,\text{mA}$$